# **Application Note**

650V IGBT

Geen Power Module(GPM) 3

Application Note

RSN3\*\*07F / RSN3\*\*07FT

#### Table of contents

- 1. Introduction

- 1.1 Application

- 1.2 Lineup

- 1.3 Features

- Specifications

- 2.1 Inverter Part

- 2.2 Bootstrap Diode

- 2.3 Control Part

- 2.4 Recommended Operating Ranges

- 3. Protection Features and Operating Sequence

- 3.1 Under Voltage Lockout Protection (UVLO)

- 3.1.1 Low-side UVLO Sequence

- 3.1.2 High-side UVLO Sequence

- 3.2 Over-temperature Protection

- 3.3 Short Circuit (SC) Protection Sequence

- 4. Application

- 4.1 Application Circuit Example

- 4.2 Bootstrap Circuit

- 4.2.1 Basic Charging Scheme

- 4.2.2 Initial Charging

- 4.2.3 Selection of Bootstrap Capacitance of CBS

- 4.3 Determination of Shunt Resistance

- 4.3.1 Shunt Resistance

- 4.3.2 Recommended Wiring Method around Shunt Resistor

- 4.3.3 RC Filter Time Constant

- 4.4 Temperature Output Function Vot

- 4.4.1 VoT Output Circuit

- 4.4.2 In the case of Low Voltage Controller

- 4.4.3 In the case of Protection Level Higher than MCU Supply Voltage

- 4.4.4 In the case of Detecting Lower Temperature than Room Temperature

- 4.5 Signal Input Terminals

- 4.6 Fault Output Terminals

- 4.7 PCB Layout Guidance

- 4.8 Heat Sink Mounting

- 4.8.1 Tightening Torque

- 4.8.2 Handling Precautions

- 4.8.3 Mounting to Substrate

- Package

- 5.1 Outline Drawing

- 5.2 Marking

- 5.3 Packaging Specification

- 6. Revision History

### 1. Introduction

## 1.1 Application

- Air-conditioner, Washing machine etc.

- Motor control for Industrial Motor (AC 200 V Class)

### 1.2 Lineup

Table. 1 Lineup

| Series | Part Number | Rating | Option                            |

|--------|-------------|--------|-----------------------------------|

|        | RSN34007F   | 40A    |                                   |

|        | RSN33007F   | 30A    | VOT (Analog Temperature Output)   |

| GPM3   | RSN32007F   | 20A    |                                   |

| GPIVIS | RSN34007FT  | 40A    |                                   |

|        | RSN33007FT  | 30A    | OTP (Over Temperature Protection) |

|        | RSN32007FT  | 20A    |                                   |

#### 1.3 Features

- 650V / 40A 3-Phase IGBT Inverter

- Low-Losses & Short-Circuit-Rated IGBTs

- Soft Reverse Recovery Diodes

- Built-In Bootstrap Diodes

- Very Low Thermal Resistance with DBC Substrate

- Under-Voltage Lock-Out for High-Side and Low-Side

- Short-Circuit Protection (SC)

- Over temperature Protection (RSN3\*\*07F<u>T</u> only)

- LVIC Temperature Output (RSN3\*\*07F only)

- 3.3 V and 5V Input Logic Compatible : Active High

- Fault Signaling: LVIC UVLO and Short-Circuit Protection

- Isolation Rating of 1500 Vrms/1 min

- UL 1557 Certified (File E540859)

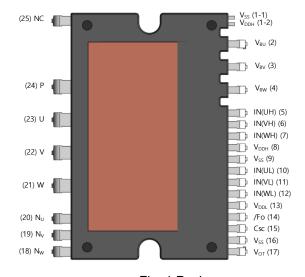

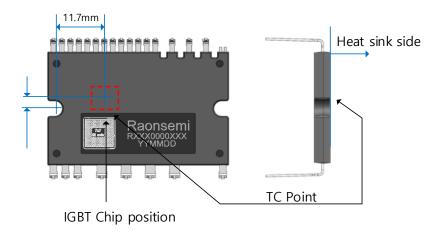

Fig. 1 Package

Fig. 2 Internal Block Diagram

## 2. Specifications

### 2.1 Inverter Part

Table, 2 Inverter Part of RSN34007F / RSN34007FT

| Syr | mbol                | Parameter                            | Cond                                                                        | litions                                     | Min.                                  | Тур. | Max. | Unit |  |    |

|-----|---------------------|--------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------|---------------------------------------|------|------|------|--|----|

| Vo  | E(sat)              | Collector-Emitter saturation Voltage | $V_{DD}=V_{BS}=15V,$<br>$V_{IN}=5V$                                         | IC=40A, Tj=25°C                             | -                                     | 1.5  | 1.8  | V    |  |    |

| ,   | √ <sub>F</sub>      | FWDi Forward Voltage                 | V <sub>IN</sub> =0V                                                         | I <sub>C</sub> =-40A, T <sub>j</sub> = 25°C | -                                     | 1.5  | 1.8  | V    |  |    |

|     | T <sub>on</sub>     |                                      |                                                                             |                                             |                                       | 1.5  |      | μs   |  |    |

|     | T <sub>C(on)</sub>  |                                      | VDV 000V VDD 45V                                                            | /                                           |                                       | 0.2  |      | μs   |  |    |

| HS  | T <sub>off</sub>    |                                      | VPN=300V, VDD=15V, Ic=40A, Tj=25°C<br>VIN=0V 5V, Inductive Load, See fig. 3 |                                             | VIN=0V 5V, Inductive Load, See fig. 3 |      |      | 1.5  |  | μs |

|     | T <sub>C(off)</sub> |                                      | (Note 1)                                                                    |                                             |                                       | 0.1  |      | μs   |  |    |

|     | T <sub>rr</sub>     | Constanting Times                    |                                                                             |                                             |                                       | 0.1  |      | μs   |  |    |

|     | Ton                 | Switching Times                      |                                                                             |                                             |                                       | 1.4  |      | μs   |  |    |

|     | T <sub>C(on)</sub>  |                                      | VDV 000V VDD 45V                                                            | /                                           |                                       | 0.2  |      | μs   |  |    |

| LS  | T <sub>off</sub>    |                                      | VPN=300V, VDD=15V<br>VIN=0V 5V, Inductive                                   |                                             |                                       | 1.4  |      | μs   |  |    |

|     | T <sub>C(off)</sub> |                                      | (Note 1)                                                                    |                                             |                                       | 0.1  |      | μs   |  |    |

|     | T <sub>rr</sub>     |                                      |                                                                             |                                             |                                       | 0.1  |      | μs   |  |    |

| I   | CES                 | Collector-Emitter leakage Current    | V <sub>ce</sub> = V <sub>ces</sub>                                          |                                             | -                                     | -    | 1    | mA   |  |    |

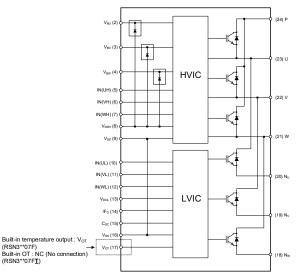

<sup>1.</sup> ton and toff include the propagation delay of the internal drive IC. tc(on) and tc(off) are the switching times of IGBT under the given gate-driving condition internally. For the detailed information, please see Fig. 3.

Switching time definition and performance test method are shown in Fig. 3 and Fig. 4 Switching characteristics are measured by half bridge circuit with inductance load.

Fig. 3 Switching Time Definition

Fig. 4 Evaluation Circuit (inductive load) IGBT Evaluation Short A for Low-side, and Short B for High-side

## 2.2 Bootstrap Diode

Table. 3 Bootstrap Diode of RSN34007F / RSN34007FT

| Symbol  | Parameter       | Cond                           | itions     | Min. | Тур. | Max. | Unit |

|---------|-----------------|--------------------------------|------------|------|------|------|------|

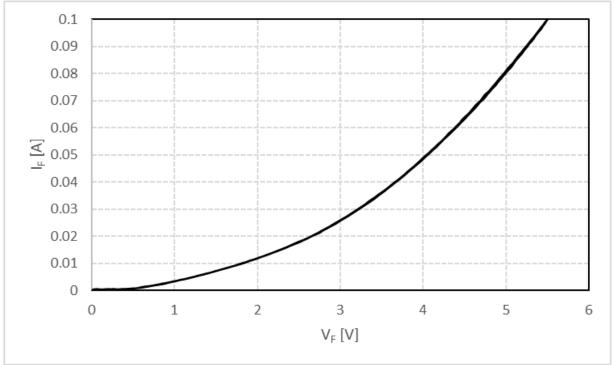

| $V_{F}$ | Forward Voltage | I <sub>F</sub> =0.01A, Tj=25°C | See Fig. 5 | -    | 1.6  | -    | ٧    |

VDD of 15 V is recommended when only the integrated bootstrap circuitry is used.

Fig. 5 Internal Bootstrap Diode IF-VF Characteristics

#### 2.3 Control Part

Table. 4 Control Part of RSN34007F / RSN34007FT

| Symbol               | Parameter                                           | Cor                                                     | nditions                                                        | Min.  | Тур. | Max.  | Unit |

|----------------------|-----------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------|-------|------|-------|------|

| $I_{\text{QDDH}}$    | Quiescent V <sub>DD</sub> Supply                    | V <sub>DDH</sub> =15V,<br>V <sub>IN(UH,VH,WH)</sub> =0V | V <sub>DDH</sub> -V <sub>SS</sub>                               | -     | -    | 0.1   | mA   |

| $I_{QDDL}$           | Current                                             | V <sub>DDL</sub> =15V,<br>V <sub>IN(UL,VL,WL)</sub> =0V | V <sub>DDL</sub> -V <sub>SS</sub>                               | -     | -    | 2.0   | mA   |

| I <sub>QBS</sub>     | Quiescent VBS Supply<br>Current                     | $V_{DD}=V_{BS}=15V,$<br>$V_{IN(UH,VH,WH)}=0V$           | $V_{BU}$ - $V_{SU}$ , $V_{BV}$ - $V_{SV}$ , $V_{BW}$ - $V_{SW}$ | -     | -    | 0.1   | mA   |

| $V_{FOH}$            | Foult Output Valtage                                | V <sub>DD</sub> =15V, Vsc=0V, V<br>Pull-up              | / <sub>FO</sub> Circuit: 10kΩ to 5V                             | 4.90  | -    | -     | V    |

| $V_{FOL}$            | Fault Output Voltage                                | V <sub>DD</sub> =15V, Vsc=1V, II                        | FO=1mA                                                          | -     | -    | 0.95  | V    |

| $V_{\text{SC(ref)}}$ | Short Circuit Trip Level (Note 2)                   | V <sub>DDH</sub> =V <sub>DDL</sub> =15V                 | C <sub>SC</sub> -V <sub>SS</sub>                                | 0.455 | 0.48 | 0.505 | V    |

| $U_{VDDD}$           |                                                     | Detection Level                                         |                                                                 | 10.3  | -    | 12.5  | V    |

| $U_{VDDR}$           | Supply Circuit Under-                               | Reset Level                                             |                                                                 | 10.8  | -    | 13.0  | V    |

| $U_{VBSD}$           | Voltage Protection                                  | Detection Level                                         |                                                                 | 10.0  | -    | 12.0  | V    |

| $U_{VBSR}$           |                                                     | Reset Level                                             |                                                                 | 10.5  | -    | 12.5  | V    |

| I <sub>IN</sub>      | Input Current (Note3)                               | V <sub>IN</sub> =5V                                     |                                                                 | 0.7   | 1.0  | 1.5   | mA   |

| V <sub>IN(ON)</sub>  | ON Threshold Voltage                                | Applied between V <sub>IN</sub>                         | wuh vh wh)-Vss.                                                 | -     | -    | 2.6   | V    |

| $V_{\text{IN(OFF)}}$ | OFF Threshold Voltage                               | V <sub>IN(UL,VL,WL)</sub> -V <sub>SS</sub>              | ,, -3/                                                          | 0.8   | -    | -     | V    |

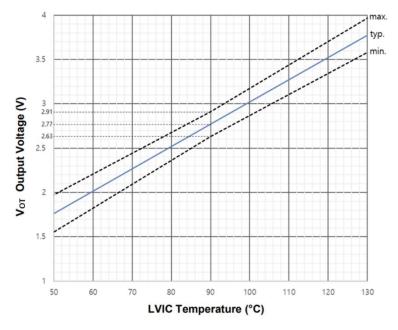

| V <sub>OT</sub>      | Voltage Output for LVIC<br>Temperature Sensing Unit | VDDL=15V, TLVIC=<br>See from Fig. 20 to                 |                                                                 | 0.88  | 1.13 | 1.39  | V    |

| t <sub>FOD</sub>     | Fault-Out Pulse Width                               |                                                         |                                                                 | 20    | -    | -     | us   |

<sup>2.</sup> Short-circuit current protection functions only at the low-sides because the sense current is divided from main current at low-side IGBTs. Inserting the shunt resistor for monitoring the phase current at NU, NV, NW terminal, the trip level of the short-circuit current is changed.

## 2.4 Recommended Operating Ranges

Table. 5 Recommended Operating Ranges of RSN34007F / RSN34007FT

| Symbol              | Parameter                                   | Conditions                                | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------------|-------------------------------------------|------|------|------|------|

| VPN                 | Supply Voltage                              | Applied between P-NU, NV, NW              | ı    | 300  | 400  | V    |

| VDD                 | Control Supply Voltage                      | Applied between VDDH-VSS, VDDL-VSS        | 13.5 | 15.0 | 16.5 | V    |

| VBS                 | High-Side Control Bias<br>Voltage           | Applied between VBU-VSU, VBV-VSV, VBW-VSW | 13.0 | 15.0 | 18.5 | V    |

| dVDD/dt,<br>dVBS/dt | Control Supply Variation                    |                                           | -1   | -    | +1   | V/µs |

| tdead               | Blanking Time for<br>Preventing Arm – Short | For Each Input Signal                     | 1.0  | -    | -    | μs   |

| FPWM                | PWM Input Signal                            | -40°C≤TC≤125°C, -40°C≤Tj≤150°C            | -    | -    | 20   | kHz  |

| PWIN(ON)            | Minimum Input Pulse                         | Con Fig. 20 (Note F)                      | 0.7  | -    | -    |      |

| PWIN(OFF)           | Width                                       | See Fig. 28 (Note 5)                      | 0.7  | _    | _    | μs   |

| Tj                  | Junction Temperature                        |                                           | -40  | -    | +150 | °C   |

<sup>5.</sup> This product might not make output response if input pulse width is less than the recommended value.

<sup>3.</sup> RC coupling at each input might change depending on the PWM control scheme used in the application and the wiring impedance of the application's printed circuit board. The input signal section integrates 5kΩ(typ.) pull-down resistor. Therefore, when using an external filtering resistor, please pay attention to the signal voltage drop at input terminal.

<sup>4.</sup> T<sub>LVIC</sub> is LVIC temperature and VOT is only for sensing temperature of LVIC and cannot shutdown IGBTs automatically. The relationship between VOT voltage output and LVIC temperature is described in Fig. 5. It is recommended to add a ceramic capacitor of 10nF or more between VOT and VSS (Signal Ground) to make the VOT more stable. Refer to the application note for this products about usage of VOT.

## 3. Protection Features and Operating Sequence

## 3.1 Under Voltage Lockout Protection (UVLO)

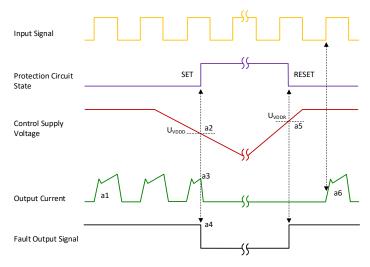

### 3.1.1 Low-side UVLO Sequence

The reduction of control power supply voltage causes the gate voltage of IGBTs to drop and IGBTs rapid increased losses. To avoid this the UVLO function is implemented. Both the floating power supply (VBS) of HVIC and the control power supply (VCC) of LVIC have UVLO function. However, only LVIC power supply activate the FO output signal.

Fig. 6 Under-voltage Protection (Low-side)

- a1: Normal operation: IGBT ON and carrying current.

- a2: Under-voltage detection (UVDDD).

- a3: IGBT OFF in spite of control input condition.

- a4: Fault output operation starts.

- a5: Under-voltage reset (UVDDR).

- a6: Normal operation: IGBT ON and carrying current by triggering next signal from LOW to HIGH.

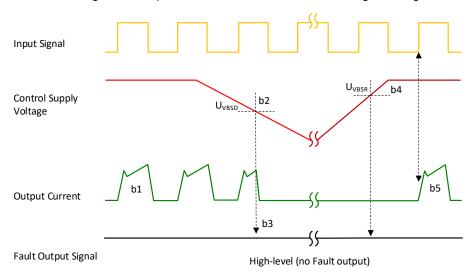

### 3.1.2 High-side UVLO sequence

The HVIC operates in under voltage lockout protection mode but does not change the signal on the /FO pin.

Fig. 7 Under-voltage Protection (High-side)

- b1: Normal operation: IGBT ON and carrying current.

- b2: Under-voltage detection (UVBSD).

- b3: IGBT OFF in spite of control input condition, but there is no fault output signal.

- b4: Under-voltage reset (UVBSR).

- b5: Normal operation: IGBT ON and carrying current by triggering next signal from LOW to HIGH.

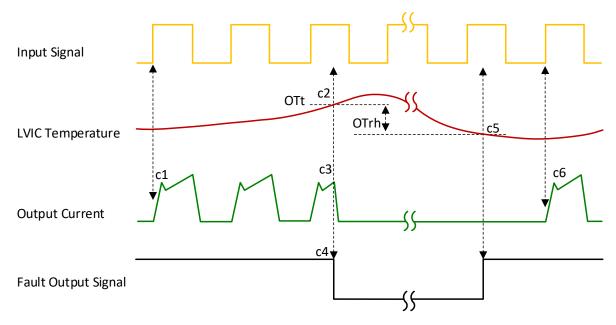

## 3.2 Over-temperature Protection

GPM has thermal shutdown by monitor the LVIC temperature. In case the LVIC temperature exceeds and keeps over the thermal shutdown trip level, the FO open drain is activated and all low side IGBTs turn off.

Table. 6 Over-temperature of RSN3400FT, T option version only

| Item                   | Symbol | Conditions               | Min. | Тур. | Max. | Unit |

|------------------------|--------|--------------------------|------|------|------|------|

| Trip Temperature       | OTt    | Monitor LVIC temperature | -    | 140  | -    | ℃    |

| Hysteresis temperature | OTth   | Monitor LVIC temperature | -    | 10   | -    | ℃    |

Fig. 8 Over-temperature Protection

- c1. Normal operation. IGBT ON and outputs current Ic.

- c2. LVIC temperature exceeds OT trip level(OT<sub>t</sub>).

- c3. All low side IGBTs turn off despite control input condition.

- c4. Fault output operation starts.

- c5. LVIC temperature drops to OT reset level.

- c6. Normal operation: IGBT ON and carrying current by triggering next signal form LOW to HIGH.

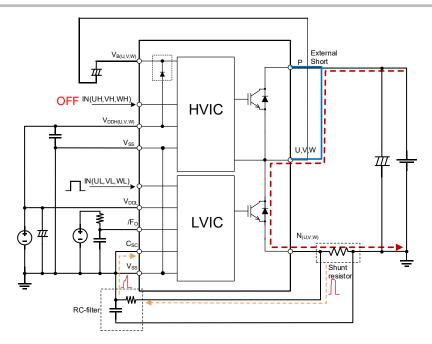

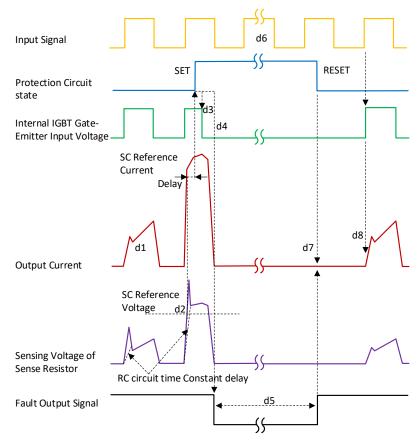

## 3.3 Short Circuit (SC) Protection Sequence

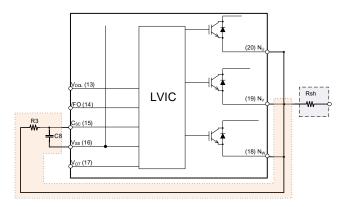

GPM3 use external shunt resistor for the current detection as shown in Fig. 9. The internal protection circuit inside the IC captures the excessive large current by comparing the  $C_{SC}$  voltage generated at the shunt resistor with the referenced SC trip voltage, and perform protection automatically. The threshold voltage trip level of the SC protection  $V_{SC(ref)}$  is type. 0.48V.

In cause of SC protection happens, all gates of Low-side three phase IGBTs will be interrupted together with a fault signal output. High-side three phase IGBT gate operation is unrelated to SC protection mode. In order to stop all IGBTs, the protection mode must be activated by monitoring the current using a microcontroller.

To prevent GPM3 erroneous protection due to normal switching noise and/or recovery current, it is necessary to set an RC filter (time constant :  $1.2\mu s - 2us$ ) to the C<sub>SC</sub> terminal input (Fig. 9). Also please make the pattern wiring around the shunt resistor as short as possible.

Fig. 9 Short-circuit Protection Test Circuit

Fig. 10 Short-circuit Current Protection (Low-side Operation Only) (With the External Sense Resistance and RC Filter Connection)

- d1: Normal operation: IGBT ON and carrying current.

- d2: Short-circuit current detection (SC trigger).

- d3: All low-side IGBTs turn OFF.

- d4: Fault output signal to LOW

- d5: Fault output operation starts with a fixed pulse width (min. 20us)

- d6: Input HIGH IGBT ON state, but during the active period of fault output, the IGBT doesn't turn ON.

- d7: Fault output operation finishes, but IGBT doesn't turn on until triggering the next signal from LOW to HIGH.

- d8: Normal operation: IGBT ON and carrying current.

## 4. Application

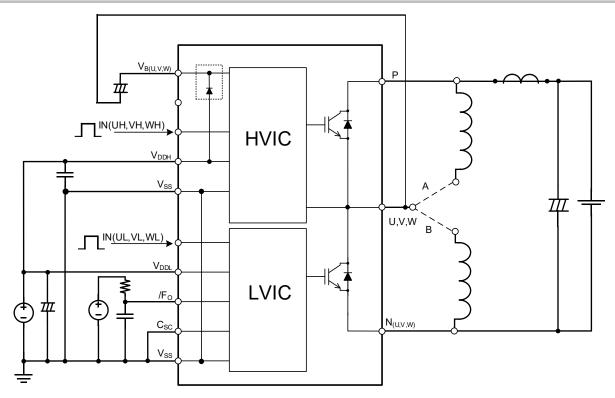

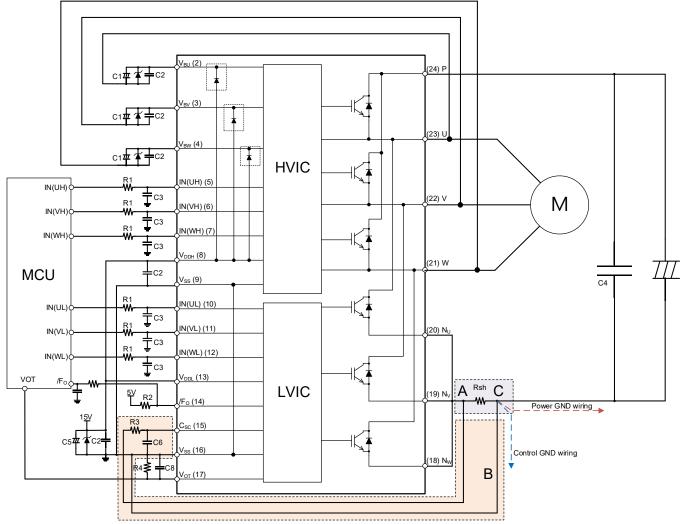

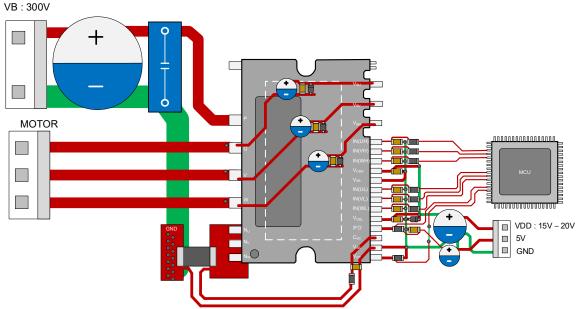

### 4.1 Application Circuit Example

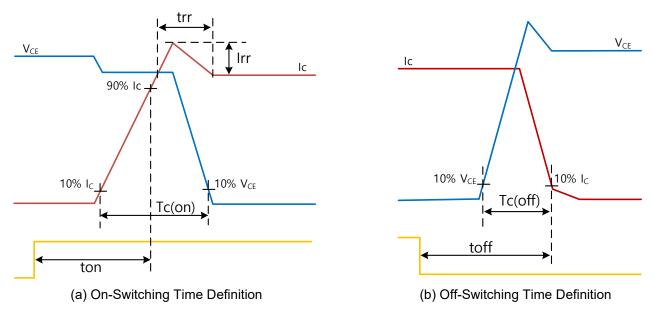

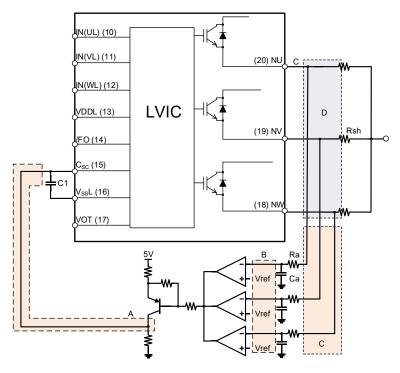

Fig. 11 Application Circuit

#### NOTES (6):

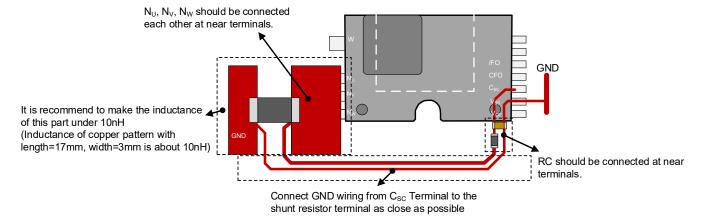

- a. If control GND is connected with power GND by common broad pattern, it may cause malfunction by power GND fluctuation. It is recommended to connect control GND and Power GND at only a point C (near the terminal of shunt resistor).

- b. To avoid malfunction, the wiring of each input should be as short as possible (less than 2-3 cm)

- c. /FO output is an open-drain type. This signal line should be pulled up resistor to the positive side of the MCU or control power supply with a resistor that makes IFO up to 1 mA. (In the case of pulled up to 5V, R2 = 10 k $\Omega$  is recommended.) Please refer to Fig. 31.

- d. Input signal is active-HIGH type. There is a 5 k $\Omega$  resistor inside the IC to pull-down each input signal line to GND. RC coupling circuits should be adopted for the prevention of input signal oscillation. RC time constant should be selected in the range 50~150 ns (recommended R1 = 100 $\Omega$ , C3 = 1 nF). Please refer to Fig. 30.

- e. Each wiring pattern inductance of point A should be minimized (recommend less than 10 nH). Use the shunt resistor Rsh of surface mounted (SMD) type to reduce wiring inductance. To prevent malfunction, wiring of point A should be connected to the terminal of the shunt resistor Rsh as close as possible.

- f. To insert the shunt resistor to measure each phase current at NU, NV, NW terminal, it makes to change the trip level ISC about the short-circuit current.

- g. To prevent errors of the protection function, the wiring of point B should be as short as possible.

- h. For stable protection function, use the sense resistor Rsh with resistance variation within 1% and low inductance value.

- i. In the short-circuit protection circuit, select the RC time constant of protection circuit in the range 2.0~2.5 μs.

- j. Each capacitor C2, C3, C6 should be mounted as close to the pins of the GPM product as possible.

- k. To prevent surge destruction, the wiring between the smoothing capacitor C4 and the P & GND pins should be as short as possible. The use of a high-frequency non-inductive capacitor of around 0.1~0.22 μF between the P

& GND pins is recommended.

- I. Relays are used in most systems of electrical equipment in industrial application. In these cases, there should be sufficient distance between the MCU and the relays.

- m. The Zener diode or transient voltage suppressor should be adopted for the protection of ICs from the surge destruction between each pair of control supply terminals (recommended Zener diode is 22V/1W, which has the lower Zener impedance characteristic than about 15  $\Omega$ ).

- n. C5 of around seven times larger than bootstrap capacitor C1 is recommended.

- o. Please choose the electrolytic capacitor with good temperature characteristic in C1. Choose 0.1~0.2μF R-category ceramic capacitors with good temperature and frequency characteristics in C2.

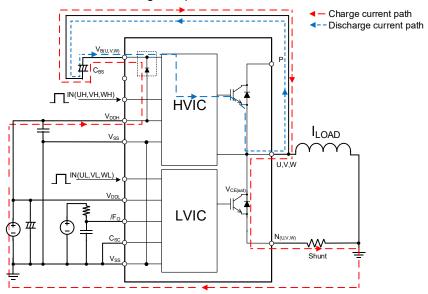

### 4.2 Bootstrap Circuit

### 4.2.1 Basic Charging Scheme

Bootstrapping is a common method for charge pumping from a low potential to a higher one. With this technique a supply voltage can be easily established for a floating high side section of the gate driver. Fig. 11 below shows a simple bootstrap circuit diagram. It represents only one-phase effective circuit from a three-phase half bridge inverter. The bootstrap functionality is implemented internally to limit current.

•

$$V_{BS} = V_{DD} - V_F - V_R - V_{CE(sat)}$$

where:

VDD: supply voltage of gate driver.

VF: bootstrap diode forward voltage drop.

VR : bootstrap resistor voltage drop

VCE(sat)max: maximum emitter collector voltage drop of low-side IGBT.

Fig. 12 Bootstrap Circuit

#### 4.2.2 Initial Charging

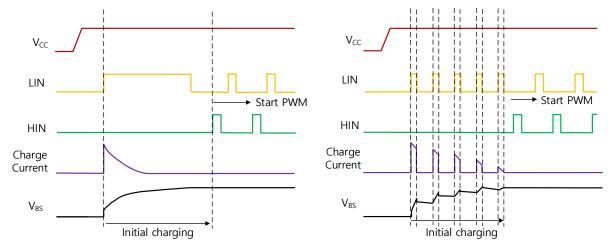

In bootstrap circuit, it is necessary to charge to the bootstrap capacitor (C<sub>BS</sub>) initially. C<sub>BS</sub> charging is performed by turning on all low side IGBT normally. When outer load(e.g. motor) is connected to IPM, C<sub>BS</sub> charging may be performed by turning on only one phase low side IGBT since potential of all output pins will go down to GND level through motor windings.

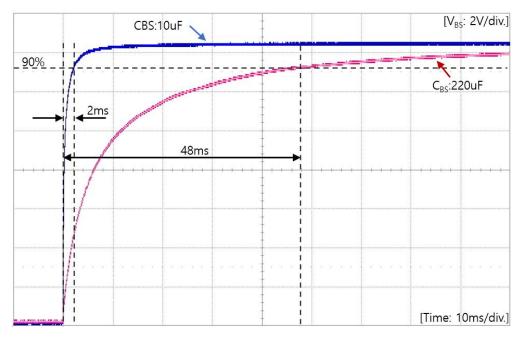

However, its charging efficiency might become lower due to some reason. (e.g. wiring resistance of motor). There are mainly two procedures for  $C_{BS}$  charging. One is performed by one long pulse (Fig. 13(a)), and another is conducted by multiple short pulse (Fig. 13(b)). Multi pulse method is used in case of some restriction like control supply capability. Necessary time of initial charging depends on the capacitance of  $C_{BS}$  (Fig. 13) and current limiting circuit. After a detailed evaluation on the actual application, please secure enough charge time depending on  $C_{BS}$  capacitance.

- (a) Waveform by one charging pulse

- (b) Waveform by multiple charging pulses

Fig. 13 Example of Waveform Initial Charging Sequence

Initial charging needs to be performed until voltage of V<sub>BS</sub> exceeds recommended minimum supply voltage 13V. (It is recommended to charge as high as possible with consideration for voltage drop between the end of charging and start of inverter operation.)

After  $V_{BS}$  was charged, it is recommended to input one ON pulse to the P-side input for reset of internal IC state before starting system. Necessary width is allowable minimum input pulse width  $P_{WMIN}(on)$  or more.

Fig. 14 Waveform Charging Voltage of V<sub>BS</sub>

#### 4.2.3 Selection of Bootstrap Capacitance of CBS

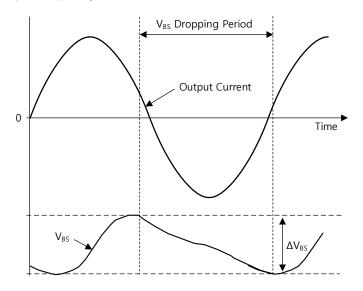

The bootstrap capacitance should be selected according to the operating conditions to avoid unexpected undervoltage protection. The ripple voltage of  $V_{BS}$  ( $\Delta V_{BS}$ ) is influenced by discharging current of gate driver, switching frequency, output current and output frequency.

Fig. 15 V<sub>BS</sub> vs. Output current waveform

Fig.15 shows an example of the ripple voltage during operation, and the voltage drop time is about 60% of the output current cycle. The voltage drop for this period equals the ripple voltage at this condition.

The recommended  $\Delta V_{BS}$  is 1.0 V and  $C_{BS}$  can be calculated by:

$$C_{BS} = \frac{I_{Discharge} * \Delta t}{\Delta V_{BS}}$$

Where:

IDischarge: Discharge current of gate driver

Δt: V<sub>BS</sub> drop time = output current cycle x dropping time ratio

$\Delta V_{\text{BS}}$  : The ripple voltage

Condition: RSN34007FT,  $V_{DD}$  =15V, fc=15kHz, fo=60Hz, three phase modulation sine wave control C<sub>BS</sub> under given conditions can be calculated roughly as:

•

$$C_{BS} = (0.75 \text{[mA]} \times 16.6 \text{ [ms]} \times 60 \text{ [\%]}) \div 1.0 \text{ [V]} = 7.47 \text{ [uF]}$$

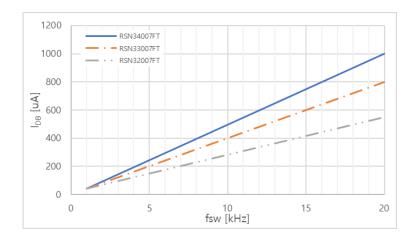

Discharge current for RSN34007FT is 0.6 mA, which is charted in Fig. 16. It indicates typical discharging current vs. switching frequency for all GPM3. The high switching frequency and the high current rating products consume larger current.

Fig. 16 Discharging current vs. switching frequency (typical value @ V<sub>DD</sub>=V<sub>BS</sub>=15V, Tj=125°C)

When designing capacitance of  $C_{BS}$ , it is necessary to consider various conditions such as operating conditions, tolerance of capacitance, and temperature characteristics of capacitance, DC bias and life time, and the tolerance of bootstrap circuit current of IC. For example,  $2 \sim 3$  times capacitance is recommended, which makes a 1.0 V voltage drop under typical conditions. In the above case, the calculated  $C_{BS}$  is 6  $\mu$ F, so a value above 12  $\sim$  18  $\mu$ F, which is 2  $\sim$  3 times the 6  $\mu$ F, is the target value. This estimation method is only an example under given conditions. If conditions are changed, the dropping period can be changed. Also, capacitance might have to be increased due to the characteristics of  $C_{BS}$  types. Therefore, sufficient evaluation in the real system is needed.

#### 4.3 Determination of Shunt Resistance

#### 4.3.1 Shunt Resistance

The value of current sensing resistance is calculated by the following expression:

•  $R_{Shunt} = V_{SC(ref)} / I_{SC}$

Where,

R<sub>Shunt</sub>: current sensing resistor value

V<sub>SC(ref)</sub>: referenced SC trip voltage

Isc: short-circuit current level

The maximum  $I_{SC}$  trip level  $I_{SC(max)}$  should be set less than the IGBT minimum saturation current which is 1.6 times as large as the rated current. For example, the  $I_{SC(max)}$  of GPM3 should be set to 40X1.6=64A or less. The parameters ( $V_{SC(ref)}$ ,  $R_{shunt}$ ) tolerance should be considered when designing the  $I_{SC}$  tip level.

For example of GPM, there is ±0.025V tolerance in the spec of V<sub>SC(ref)</sub> as shown in Table 8.

Table. 8 VCS(ref) Specification of RSN34007F / RSN04007FT

| Condition                          | Min.  | Тур. | Max.  | Unit |

|------------------------------------|-------|------|-------|------|

| At Tj =25°C, $V_{DDH}=V_{DDL}=15V$ | 0.455 | 0.48 | 0.505 | V    |

Then, the range of I<sub>SC</sub> trip level can be calculated by the following expressions:

- Isc(max) = Vsc(ref)max / Rshunt(min)

- $I_{SC(typ)} = V_{SC(ref)typ} / R_{Shunt(typ)}$

- Isc(min) = Vsc(ref)min / Rshunt(max)

If choose to shunt resistor in  $6.7m\Omega$  and  $\pm 5\%$  tolerance. So. The I<sub>SC</sub> trip range is described as Table 9.

Table. 9 Example CSC Trip Ranges

| Condition                                            | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|------|------|------|------|

| At Tj =25°C, V <sub>DDH</sub> =V <sub>DDL</sub> =15V | 64.4 | 71.6 | 79.3 | Α    |

#### 4.3.2 Recommended Wiring Method around Shunt Resistor

External shunt resistor is employed to detect short-circuit accident, A longer wiring between the shunt resistor and GPM3 causes so much large surge that might damage built-in IC. To decrease the pattern inductance, the wiring between the shunt resistor and GPM3 should be as short as possible and using low inductance type resistor such as SMD resistor instead of long-lead type resistor.

Fig. 17 External SC Protection Circuit with Shunt Resistors

Fig. 18 Example One-shunt Resistors PCB

Fig. 19 External SC Protection Circuit with Three-shunt Resistors

#### NOTES (7):

- a. It is necessary to set the time constant RaCa of external comparator input so that IGBT stop within 2us when short circuit occurs. SC interrupting time might vary with the wiring pattern, comparator speed and so on.

- The Threshold voltage Vref should be set up the same rating of short circuit trip level (C<sub>SC</sub>(ref)typ 4.8V).

- c. Select the external shunt resistance so that SC trip-level is less than specified value specified in the datasheet of each product.

- d. To avoid malfunction, the wiring A,B,C should be as short as possible.

- e. The point D at which the wiring to comparator is divided should be near the terminal of shunt resistor.

- OR output high level should be over 0.505V (=maximum V<sub>SC(ref)</sub>).

- g. GND of comparator, Vref circuit and Ca should be not connected to noisy power GND but to control GND wiring.

#### 4.3.3 RC Filter Time Constant

It is necessary to set an RC filter in the short-circuit current sensing circuit in order to prevent malfunction of short-circuit protection due to noise interference. The RC time constant is determined on the applying time of noise interference and the SCSOA of the GPM3.

When the voltage drop on the external shunt resistor exceeds the short-circuit trip level, the (t<sub>Filter</sub>) that the C<sub>SC</sub> terminal voltage rises to referenced short-circuit trip level can be calculated by the following expression:

•

$$V_{SC} = R_{Shunt} \times I_C \times (1 - \varepsilon^{\left(\frac{t_{Filter}}{\tau}\right)})$$

•

$$t_{Filter} = -\tau \times \ln \left(1 - \frac{v_{SC}}{R_{Shunt} \times I_C}\right)$$

Where.

Vsc: CSC terminal input voltage

τ : RC time constant I<sub>C</sub> : peak current

On the other hand, the typical time delay  $t_{Dealy}$  (from  $V_{SC}$  voltage reaches  $V_{SC(ref)}$  to IGBT gate shutdown) of IC is shown in Table 10.

Table. 10 t<sub>Dealy</sub> Specification of RSN34007F / RSN34007FT

| Item                           | Min. | Тур. | Max. | Unit |

|--------------------------------|------|------|------|------|

| Propagation Delay (delay time) | -    | -    | 600  | ns   |

Therefore, the total delay time from occurrence of the short-circuit event to the shutdown of the IGBT gate becomes:

The  $t_{total}$  delay must be less than 5µs of the short circuit withstand time (tSC), which is specified in the datasheet. Thus, the RC time constant should be set in the range of 1~2µs.

## 4.4 Temperature Output Function VoT

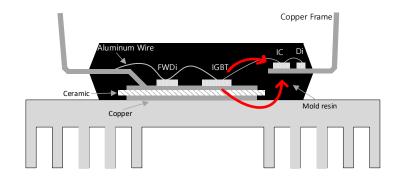

This function measures the temperature of control LVIC by built in temperature sensor on LVIC. The heat generated at IGBT and FWDi transfer to LVIC through molding resin of package and outer heat sink in Fig. 20. So LVIC temperature cannot respond to rapid temperature rise of those power chips effectively. (e.g. motor lock, short circuit) It is recommended to use this function for protecting from slow excessive temperature rise by such cooling system down and continuance of overload operation.

Fig. 20 Thermal Conduction from Power Chips

Fig. 21 T<sub>C</sub> Measurement Point

Fig. 22 VOT Output vs LVIC Temperature

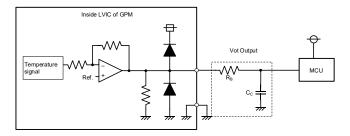

#### 4.4.1 VOT Output Circuit

VOT output is created by amplifying the temperature signal as described in Fig. 23. Fig. 23 is an example of VOT output circuit in the case of using and RC filter.

Fig. 23 VOT Output Circuit

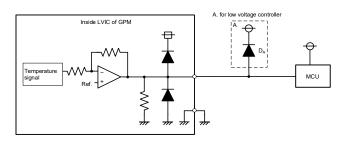

#### 4.4.2 In the case of Low Voltage Controller

In the case of using V<sub>OT</sub> with low voltage controller like 3.3V MCU, Vot output might exceed control supply voltage 3.3V when temperature rises excessively. It is recommended to insert a clamp diode between control supply of the controller and this output for preventing over voltage damage.

Fig. 24 In the case of Low Voltage Controller

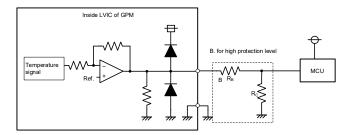

### 4.4.3 In the case of Protection Level Higher than MCU Supply Voltage

In the case of using  $V_{OT}$  with low voltage controller like 3.3V MCU, if it is necessary to set the trip VOT level to control supply voltage(e.g. 3.3V) or more. There is method of dividing the  $V_{OT}$  output by resistance voltage divider circuit and then inputting A/D converter on MCU. The dividing voltage( $V_{div.}$ ) can be calculated by the following expression:

•  $V_{div.} = R_C / (R_B + R_C)$

Fig. 25 In the case of Protection Level Higher than MCU Supply Voltage

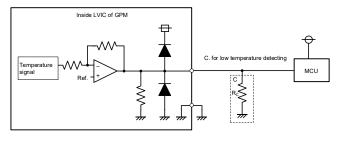

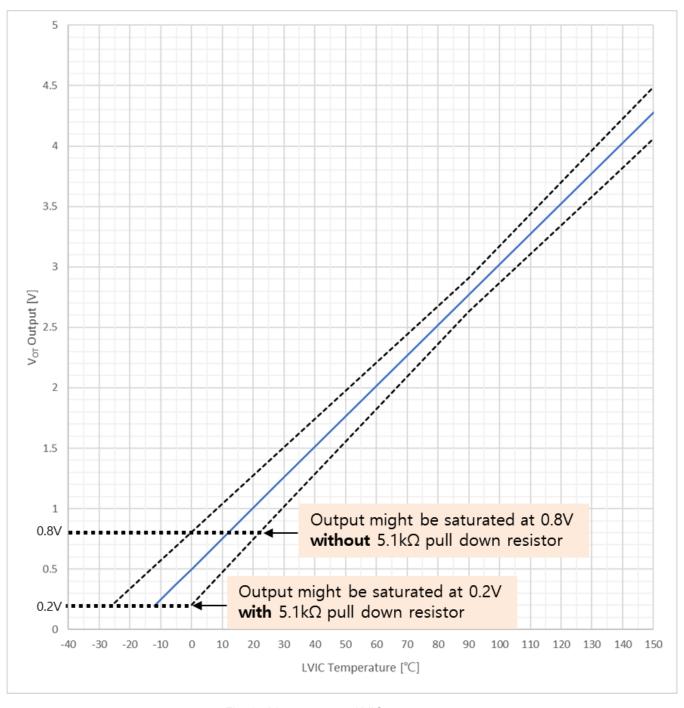

#### 4.4.4 In the case of Detecting Lower Temperature than Room Temperature

It is recommended to insert  $5k\Omega$  pull down resistor for getting linear output characteristics at lower temperature than room temperature. When the pull down resistor is inserted between  $V_{OT}$  and VSS, the extra current calculated by VOT output voltage / pull down resistance flows as LVIC circuit current continuously. In the cause of only using VOT for detecting higher temperature than room temperature, it isn't necessary to insert the pull down resistor.

Fig. 26 In the case of Detecting Lower Temperature than Room Temperature

Fig. 27  $V_{\text{OT}}$  output vs. LVIC temperature

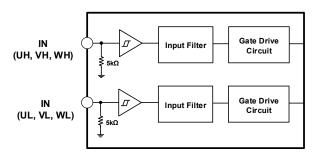

## 4.5 Signal Input Terminals

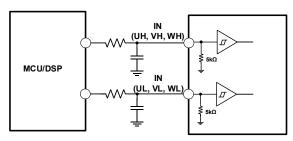

Internal circuit of control input terminals GPM3 is high-active input logic. A 5kΩ(min) pull-down resistor is built-in each input circuits of the GPM3 as shown in Fig. 28. So external pull-down resistor is not needed.

Furthermore, by lowering the turn on and turn off threshold value of input signal as shown in Table 11, a direct coupling to 3V class microcomputer or DSP becomes possible.

Fig. 28 Internal Structure of Control Input Terminals

Table. 11 Input Threshold Voltage and Minimum Pulse Width Ratings (VD =15V, Tj=25°C) of RSN34007F / RSN34007FT

| Symbol               | Parameter             | Conditions                                                                                              | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IN(on)</sub>  | On Threshold Voltage  | Applied between V <sub>IN(UH,VH,WH)</sub> -V <sub>SS</sub> , V <sub>IN(UL,VL,WL)</sub> -V <sub>SS</sub> | -    | -    | 2.6  | V    |

| V <sub>IN(OFF)</sub> | Off Threshold Voltage |                                                                                                         | 0.8  | -    | -    | V    |

| PWM(ON)              | Minimum Input Pulse   | 41.4.0                                                                                                  | 0.7  | -    | -    |      |

| PWM(OFF)             | Width                 | (Note 8)                                                                                                | 0.7  | -    | -    | μs   |

<sup>8.</sup> There are specifications for the minimum input pulse width GPM3. GPM3 might make no response if the input signal pulse width (both on and off) is less than the specified value. Please refer to the datasheet for the specification.

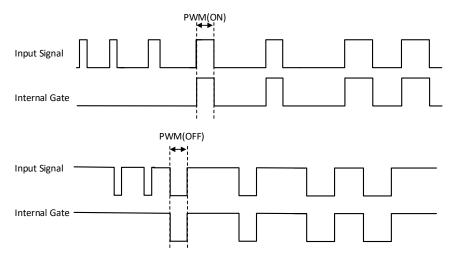

Fig. 29 Input Signal Sequence

The RC couple at each input depends on user's PWM control strategy and the wiring impedance of printed circuit board. The GPM signal input section integrates a  $5\,\mathrm{k}\Omega$  pull-down resistor, therefore, when using an external filtering resistor, please pay attention to the signal voltage drop at input terminal.

Fig. 30 Input Terminal Wiring with MCU/DSP

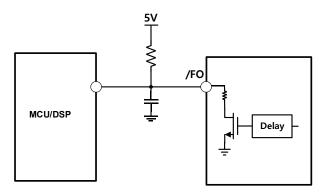

## 4.6 Fault Output Terminals

The FO pin consists in open drain output type. The device supports SCP (Short Circuit Protection), UVLO (Under Voltage Lockout) and as protection function for LVIC. When a protection function detect a malfunction, the FO open drain is activated for the period shown in Table 12 for each factor, and all low side IGBTs turn off in spite of control input condition. The device supports UVLO (Under Voltage Lockout) as protection function for HVIC, but the FO open drain is not activated. The IPM monitors the FO pin input voltage in order to turn off low side IGBTs. The low side IGBTs turn off period can be extended by external CR. (Fault pulse tuning)

Table. 12 V<sub>FO</sub> Specification of RSN34007F / RSN34007FT

| Symbol           | Parameter                | Conditions                                                   | Min. | Тур. | Max. | Unit |

|------------------|--------------------------|--------------------------------------------------------------|------|------|------|------|

| V <sub>FOH</sub> | Fault output voltage     | VSC=0V, FO terminal pulled up to 5V by $10 \mathrm{k}\Omega$ | 4.9  | 1    | 1    | V    |

| $V_{FOL}$        | Fault output voltage     | V <sub>SC</sub> =1V, I <sub>FO</sub> =1mA                    | -    | -    | 0.95 | ٧    |

| t <sub>FOD</sub> | Fault output pulse width |                                                              | 20   | ı    | -    | μs   |

Fig. 31 /FO Terminal Wiring with MCU/DSP

## 4.7 PCB Layout Guidance

In general, there are several issues to be considered when designing a switching power supply application.

- Low stray inductive connection

- Isolation distance

- Component placement This chapter will explain about the items above and come up with the solutions for the better layout design.

Fig. 32 Layout of Reference Board for 1-shunt Resistor

#### NOTES (9):

- 1. The connection between emitters of GPM inverter IPM (NU, NV, NW) and current sensing resistor should be as short and as wide as possible.

- It is recommended that the ground pin of the micro-controller should be directly connected to the V<sub>SS</sub> pin. Signal

ground and power ground should be as short as possible and connected at only one point via the VDD

capacitor.

- 3. All of the bypass capacitors should be placed as close to the pins of GPM inverter IPM as possible.

- The capacitor for voltage sensing of the current sensing resistor should be placed as close to CSC and V<sub>SS</sub> pins as possible.

- 5. In order to accurately detect the voltage of the current sensing resistor, both sensing and ground patterns should be connected at the pins of the current sensing resistor and should not be overlapped with any patterns for the load current, as shown in Fig. 32.

- 6. The snubber capacitor should be placed as close to the power terminals as possible.

- 7. The PCB routings for power pins such as P, U, V, W and NU,NV,NW should be placed on both top and bottom layers, if high current application. They have to keep the minimum isolation distance among the power patterns. The distance should be at least over than 2.54mm.

- 8. Note that there are milling profiles in gray lines on the board to keep the isolation distance.

- 9. All components except the GPM inverter IPM are placed on the top layer

### 4.8 Heat Sink Mounting

A heatsink may be required, depending on the ambient temperature or the heating of the GPM3 or its peripheral devices. Attach a heatsink as described below if necessary.

#### 4.8.1 Tightening Torque

It has the possibility to break the screw thread/hole or give damage of strain with excessive tightening torque. When over sone tightening torque point, contact thermal resistance became saturated. Following Table. 13 is the recommendation of tightening torque to avoid the device stress with optimum contact thermal resistance. Carry out a temporary bundle if needed.

Table. 13 Mechanical Characteristics and Ratings

| Recommended Screw | Recommended tightening torque | Maximum tightening torque |

|-------------------|-------------------------------|---------------------------|

| M3                | 0.69 N·M                      | 0.78 N·M                  |

#### 4.8.2 Handling Precautions

When handling this product, ensure that the environment is protected against electrostatic discharge. Package have an exposed metal portion on the same side mold surface of marking are. This portion is at the same potential as product GND pin. As necessary, please make safety provisions for insulation between package and heat sink.

#### 4.8.3 Mounting to Substrate

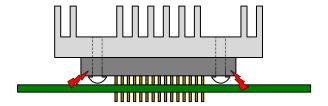

Where the GPM package is sandwiched between the heat sink and the substrate, it the static load should be no greater than 10N, The load should be spared uniformly across the device, and screw mountings should not result in substrate bending as shown in below Fig. 33 as the resulting distortion could cause device damage or failure. Consider using spacer or equivalent to attach the heat sink so as to prevent substrate bending. Also, When screwing the GPM directly to heat sink, must be careful about the torque of screwdriver.

Fig. 33 Heatsink Attachment Example

## 5. Package

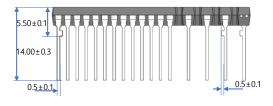

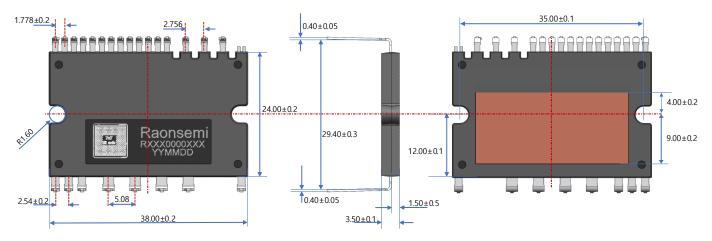

## 5.1 Outline Drawing

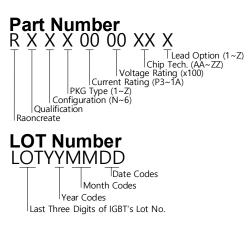

## 5.2 Marking

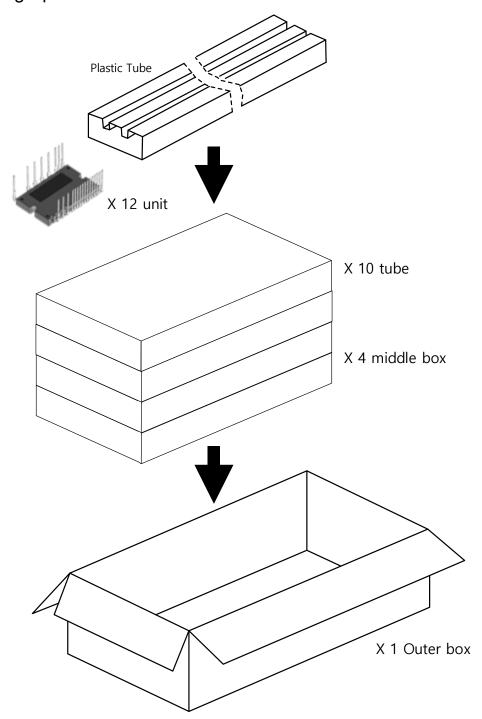

## 5.3 Packing Specification

# 6. Revision History

| Rev     | Date       | Point |

|---------|------------|-------|

| Rev 1.0 | 02/19/2025 | New   |